Shared-Memory Multiprocessors

I obtained my PhD in 1991 under the supervision of René Beaufils and Daniel Litaize. It was entitled: “Interconnection network of the M3S multiprocessor : study and design”.

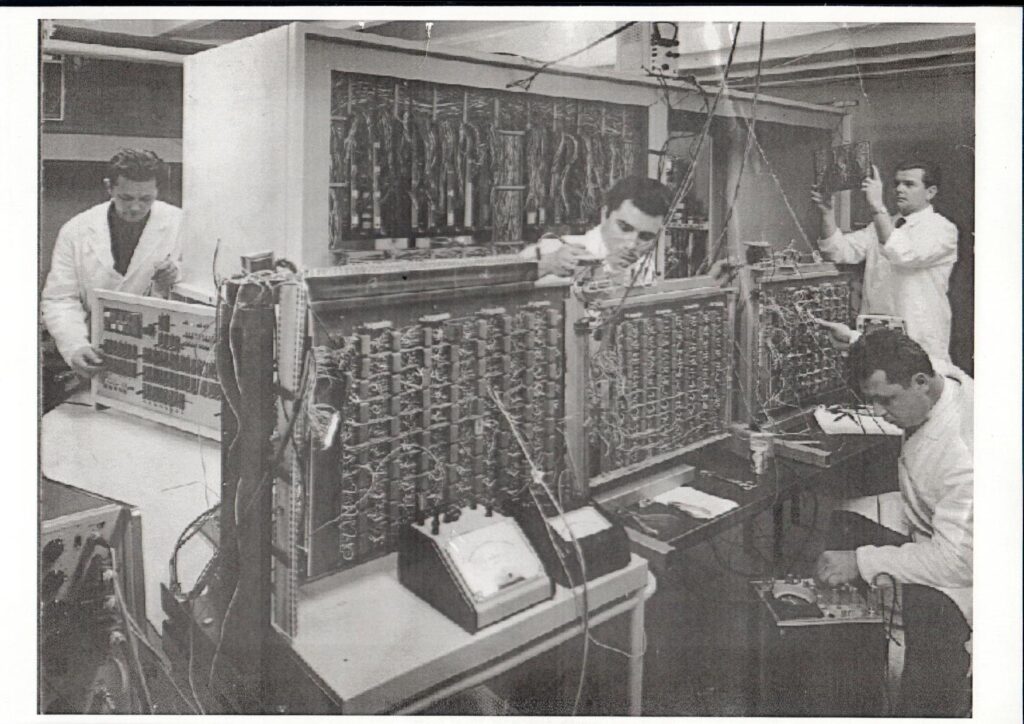

M3S [ISCA’92] was a huge project directed by Daniel Litaize aimed at realising a shared-memory multiprocessor with an interconnection network made of high-speed serial links connected to serial multiport memories [Parle’89]. I was particularly in charge of these synchronous serial links made up of AsGa chips which allow to obtain a bandwidth of 1.2 Gbit/s with an error rate less than 10-14, an incredible value at the end of the 80’s. In the multiprocessor, they were at 800Mbit/s and were demultiplexed into 16 shift registers running at 50MHz, a reasonable frequency at that time.

Superscalar Processors

While working on shared-memory multiprocessors, I noticed the progress on the processors themselves and get interested into superscalar out-of-order processors in 1994. With my PhD student Stephan Jourdan, I started to work on dimensioning such processors [ISCA’95][Micro’95] . A limiting factor is feeding the processor with instructions. With André Seznec, we proposed the multiple-block ahead branch prediction to increase the throughput of instruction fetch at a limited cost and with almost no degradation of branch prediction accuracy [Asplos96].

Predictability

Modern processors have various features whose temporal behaviour is a function of the history. This renders difficult the analysis of a program executed on such processors. We worked on various hardware or software mechanisms in order to replacer theses features by predictable ones.

We proposed a prescheduling scheme in order to simplify the analysis of an out-of-order processor [CF2005].

We also worked on the simultaneous multithreading in the context of critical systems [Samos2008].

With Thalès, I worked on the analysis of a multi-core processor in order to determine where were the interferences and what were the effects. The aim was to find hardware or software ways to avoid them.

I worked with Onera and Airbus on an execution model in order to isolate the tasks on a manycore (specifically the Kalray MPPA-256) [RTAS2016]. We are currently working on a superscalar risc-V processor where it is proved that there is no timing anomalies.