VILESCO TECHNOLOGIES

# REAL TIME CHALLENGES IN ENGINE CONTROL SYSTEMS

### RTNS'2019 27TH INTERNATIONAL CONFERENCE ON REAL-TIME NETWORKS AND SYSTEM

ENSEEIHT Toulouse, 06.11.2019 Denis Claraz – Vitesco Technologies France S.A.S.

Public

## **REAL TIME ENGINE CONTROL CHALLENGES**

**1 INDUSTRIAL CONSTRAINTS**

2 TECHNICAL CONSTRAINTS

**3 CONCLUSION**

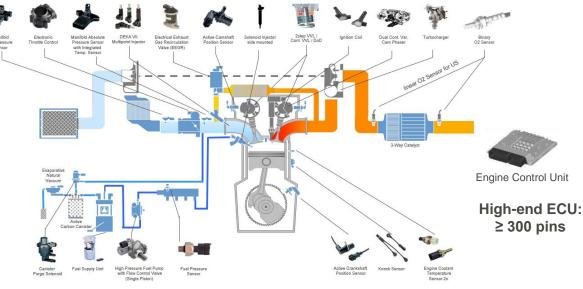

# **INTERNAL COMBUSTION ENGINE (ICE) SYSTEM OVERVIEW**

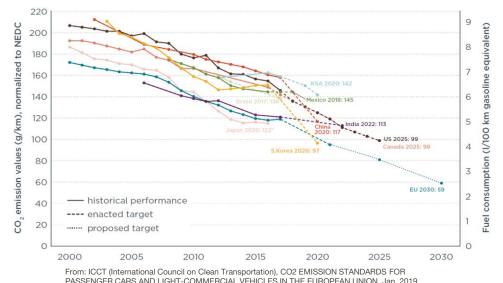

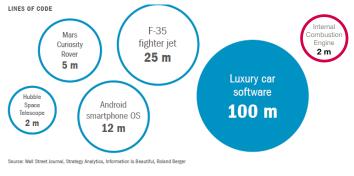

#### MAIN MARKET DRIVER IS EMISSION REDUCTION

#### GLOBAL WARMING $\Rightarrow$ CO2 EMISSION REDUCTION

$\Rightarrow$  INCREASE COMPLEXITY OF ICE SYSTEM

#### **MORE SW NEEDED TO REDUCE FUEL CONSUMPTION !**

RTNS'2019 - 27TH INTERNATIONAL CONFERENCE ON REAL-TIME NETWORKS AND SYSTEM - Toulouse, 06.11.2019 - Denis Claraz – Vitesco Technologies France S.A.S. - Public

# **AFFORDABLE SOLUTIONS**

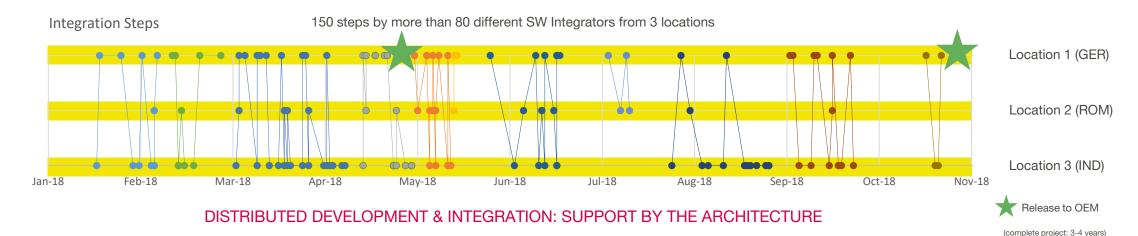

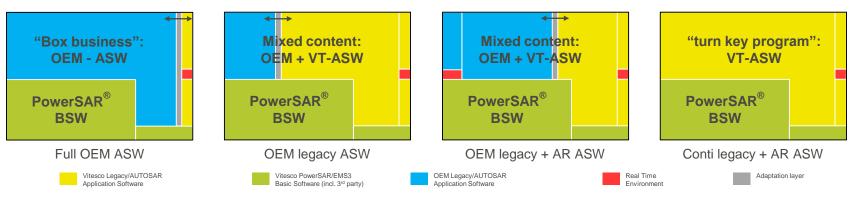

#### REUSE TO SHORTEN DEVELOPMENT CYCLES, REDUCE DEVELOPMENT COSTS

OEM DEVELOPS HIS PART INDEPENDENTLY AND INTEGRATES / BUILDS AGAIN THE SW

#### **HIGHER INTEGRATION BETWEEN PARTNERS**

ČÅŽ

## **REAL TIME ENGINE CONTROL CHALLENGES**

1 INDUSTRIAL CONSTRAINTS

**2 TECHNICAL CONSTRAINTS**

**3 CONCLUSION**

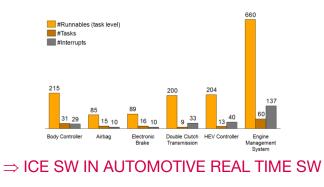

# **REAL TIME SW**

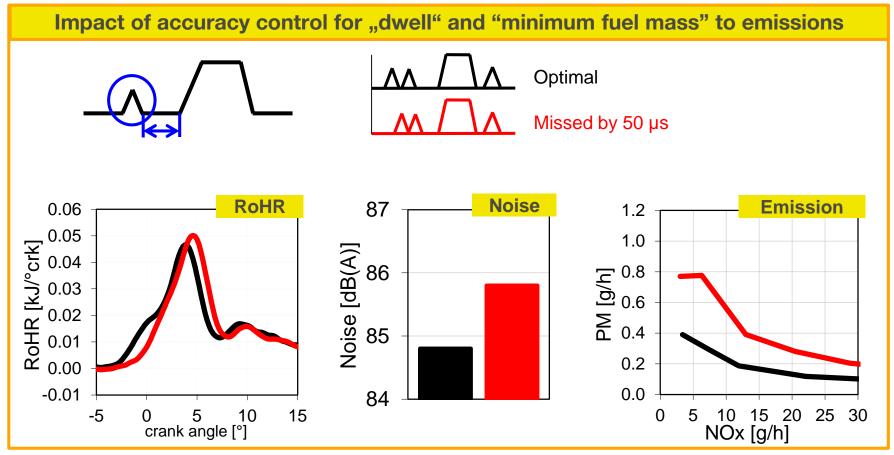

### THE RIGHT VALUE AT THE RIGHT TIME

at n= 1500 min<sup>-1</sup>, p<sub>mi</sub>= 4,2 bar, HR50= 8°KW, EGR=35%

#### **THE RIGHT TIMING IS IMPORTANT !**

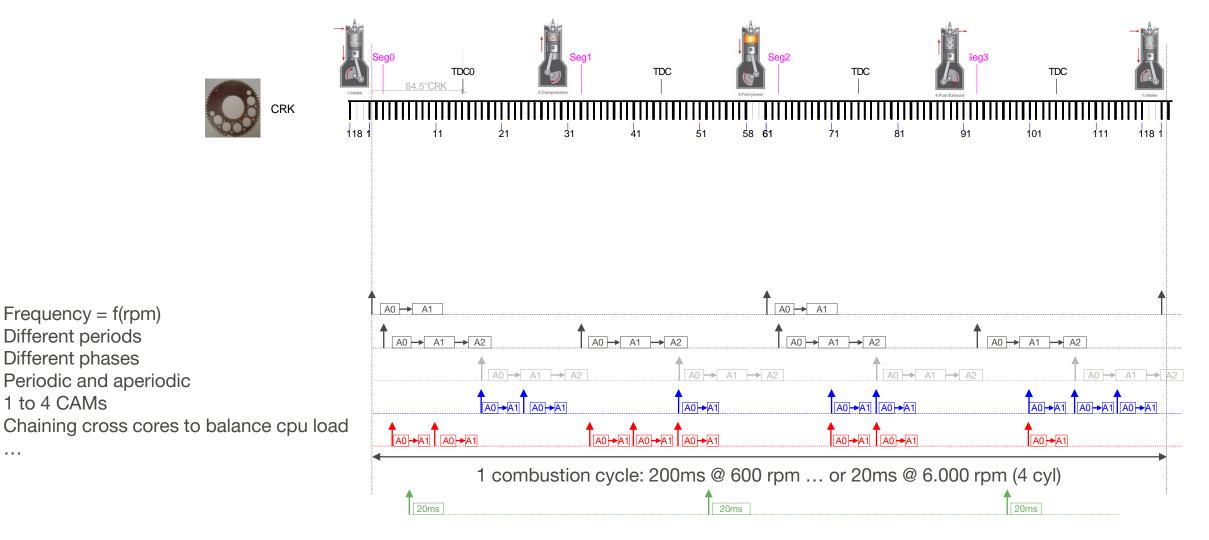

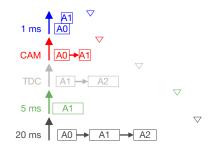

## **ANGULAR TIME**

### SW DYNAMICS DRIVEN BY ACTUATOR CONTROL DYNAMICS

#### ANGULAR TASKS AND TIME BASED TASKS RUNNING ON THE SAME CPU

RTNS'2019 - 27TH INTERNATIONAL CONFERENCE ON REAL-TIME NETWORKS AND SYSTEM - Toulouse, 06.11.2019 - Denis Claraz - Vitesco Technologies France S.A.S. - Public

1.

2.

3.

4

5.

6.

7.

. . .

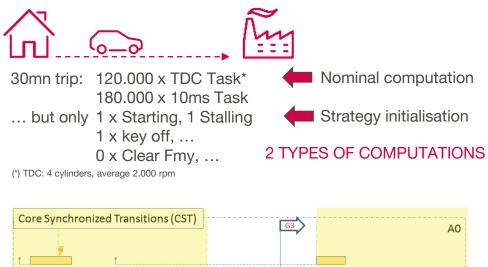

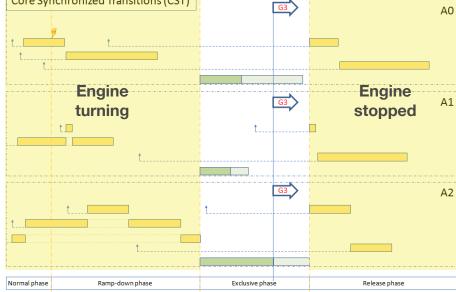

## **SPORADIC TIME**

### NEED OF COHERENT SYSTEM STATE CROSS ALL TASKS ON ALL CORES

SYSTEM TRANSITION IN A PROTECTED MODE

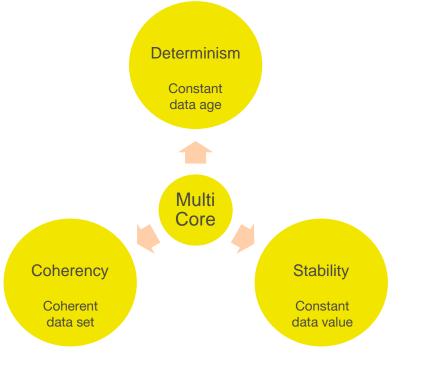

BALANCE BETWEEN 3 "TIME DOMAINS" ... ON ALL CORES

#### **DATA COMMUNICATION BETWEEN TASKS & DOMAINS TO BE CONTROLLED**

# **INTER-TASK COMMUNICATION**

### DIFFERENT TYPES OF INTEGRITY

**3 TYPES OF INTEGRITY**

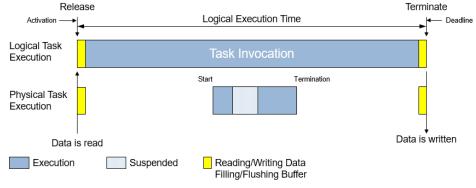

#### LOGICAL EXECUTION TIME TO ENSURE DETERMINISM

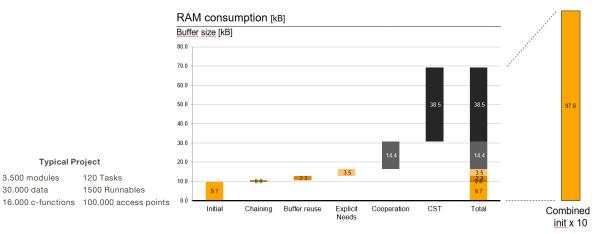

#### CRITICAL: EFFICIENCY OF BUFFERING ALGORITHM

#### **INEFFICIENT STRATEGY MAY LEAD TO ... NON-DISTRIBUTABLE SW**

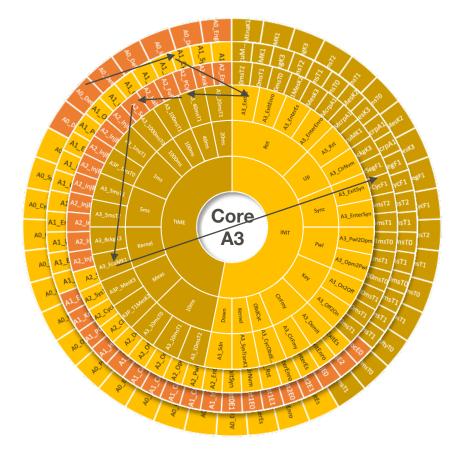

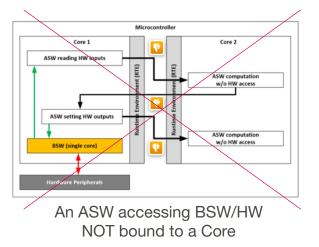

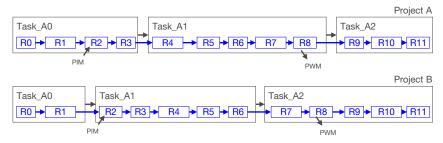

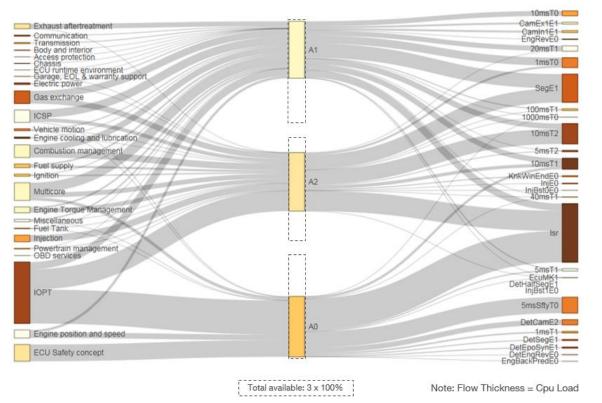

# **CORE ABSTRACTION FOR EASIER SW DISTRIBUTION**

### **3 LEVELS OF ABSTRACTION**

#### PROBLEM: CORE ALLOCATION IS A MULTI-CRITERIA CHOICE

| Event availability                                                                                                      | Link to Safety Core / Active Lockstep                                                               |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| <ul> <li>A function has a required Rate: 1<sup>st</sup> criteria for<br/>integration</li> </ul>                         | <ul> <li>Safety relevant functions have to be processed<br/>on Core with Active Lockstep</li> </ul> |

| Core affinity                                                                                                           | OEM/Other parties constraints                                                                       |

| <ul> <li>&gt; Vs. HW feature (e.g. dbl fpu,) ,<br/>other function</li> <li>&gt; OEM-SW fix some distribution</li> </ul> |                                                                                                     |

| → Limit risk for data written at different ratε                                                                         | Order of Runnables matters !                                                                        |

| Last Writer Wins (Lww) situations                                                                                       | Sequencing constraint                                                                               |

| <ul> <li>Some functions are risky to distribute (complex<br/>real time, not multi-core ready)</li> </ul>                | <ul> <li>Higher freedom for introduction of more<br/>functions in a late step</li> </ul>            |

| Distributivity of the function                                                                                          | CPU load balancing                                                                                  |

#### BSW SERVICES AVAILABLE ON EACH CORE

#### SW ARCHITECTURE INDEPENDENT OF HW FEATURES

Standard task setup for all projects despite different HW configurations (µC)

ASW INTEGRATION INDEPENDENT OF ABSTRACT CORE

#### **CORE ABSTRACTION FOR HIGHER SYNERGY BETWEEN PROJECTS, EASIER INTEGRATION**

## **REAL TIME ENGINE CONTROL CHALLENGES**

**1 INDUSTRIAL CONSTRAINTS**

2 TECHNICAL CONSTRAINTS

**3 CONCLUSION**

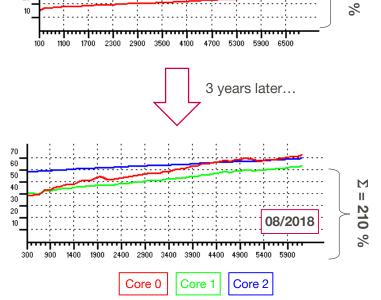

# **CORE DISTRIBUTION**

### ENSURING SYSTEM HEALTH DESPITE FUNCTIONAL CONTENT INCREASE

60

50

40

30

20

10

LOAD BALANCING PREPARES THE SYSTEM FOR FUTURE EVOLUTIONS

### (EVENT) RESPONSE TIME MONITORING IS A BETTER INDICATOR OF THE SYSTEM HEALTH

M

Ш

140

# THANK YOU FOR YOUR ATTENTION